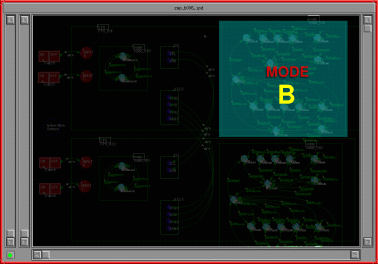

In this system, MODE B has been designed to handle the high level communications protocol between the two CPUs. Conceptually it comminucates with its counterpart MODE B on another CPU.

To view MODE B in greater detail click here

To view a detailed description of the high level comms MODE B state

machine click here

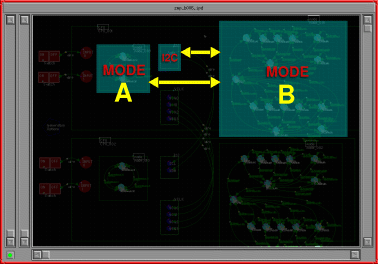

MODE B receives events from MODE A and also the I2C driver. It schedules bytes to be written to and read from the I2C driver. It operates in I2C MASTER mode when initiating a message transfer, and in I2C SLAVE mode when addressed by an I2C master.

MODE B receives events from the I2C driver when:

- the start of a message destined for this CPU has been detected

- a byte has been succesfully sent

- a transmition error has been encountered

- a start or stop condition has been received

- a byte has been received

- a busy condition is detected (traffic on the I2C bus between two or more other CPUs is detected and is in progress).

MODE A generates events for MODE B in order to initiate a message transfer.

MODE B generates events for MODE A when

- a MODE A generated message has been accepted for transmition

- transmition of a message is complete

- a message transfer if aborted due to an I2C bus error

- a message is received from another CPU

Both MODE A and MODE B transfer data between each other via a shared buffer which is external to the event system. They know when it is safe to read from or write to the buffer due to their given state. This removes the need for shared resource locks (semaphores etc) and complex polling schemes.

To view a detailed description of the high level comms MODE B state

machine click here